Ce projet consiste à créer une Mémoire cache sur le logiciel de simulation Logisim. Sincèrement, le projet n’est pas si facile que ça. Mais grâce à Logisim, ça permet d’une façon éducative et détaillée de comprendre le propre fonctionnement interne d’une mémoire cache, et comment elle est utilisée pour la mémorisation temporaire et rapide des données entre le processeur et la RAM.

Le processeur en question est un processeur 32 bits. Bien sûr, en raison de sa complexité, il n’a pas été reconstruit, seulement son port d’adresse et son port de données sont implémentés. De l’autre côté, une mémoire RAM de taille 64 Mégaoctets a été implémentée, mais pour des raisons de simplicité, une version simplifiée a été implémentée. La mémoire cache a une taille de 32 Kilo-octets, Avec une organisation interne 2-ways set associative. La politique d’écriture Write-back write policy. Et une politique de lecture Least Recently Used policy. Vous pouvez trouver plus de détails sur l’énoncé du mini-projet sur les PDF en bas.

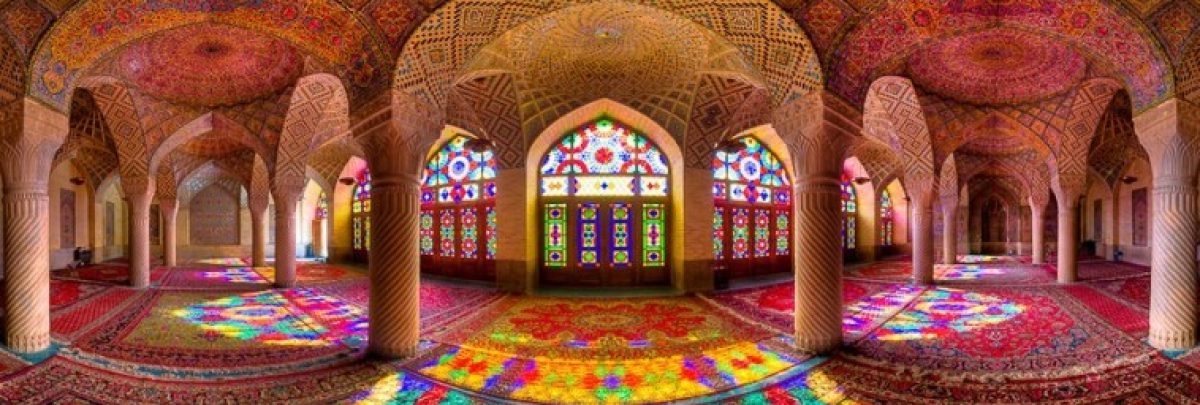

side-projectL’image suivante représente la structure hardware interne de la mémoire cache. Il est possible de cliquer sur l’image pour avoir la possibilité de zoomer et naviguer sur l’image, il est aussi possible de faire la même chose en cliquant le lien suivant.

Le lien du dépôt Github

Plus de détails et tous les fichiers du projet sont disponibles sur le dépôt GitHub : https://github.com/kara-abdelaziz/Cache-Memory-in-logisim