# Problem set 2 solution (Sequential Circuits)

# Exercise 01 :

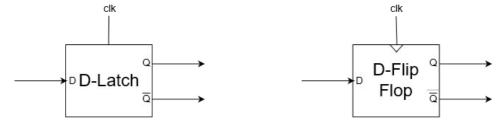

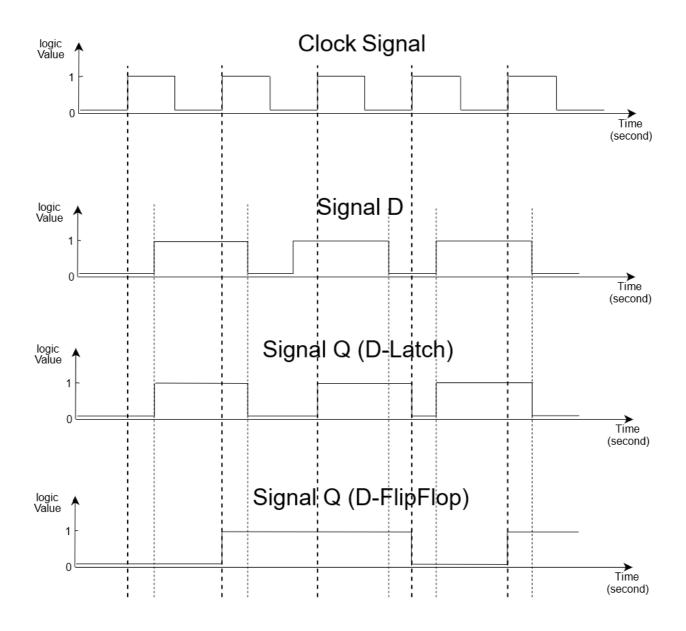

#### 2) The timing diagram of the D-Latch and the D-FlipFlop :

# Exercise 02 :

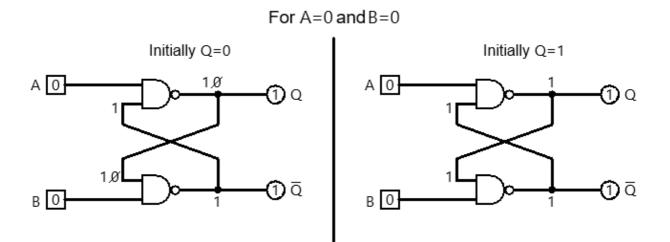

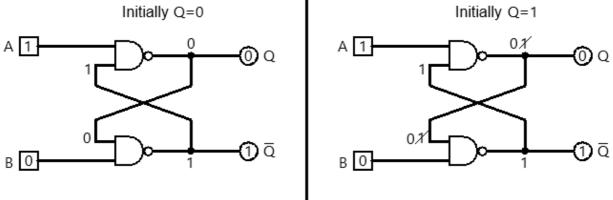

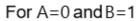

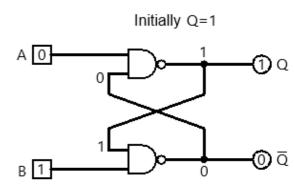

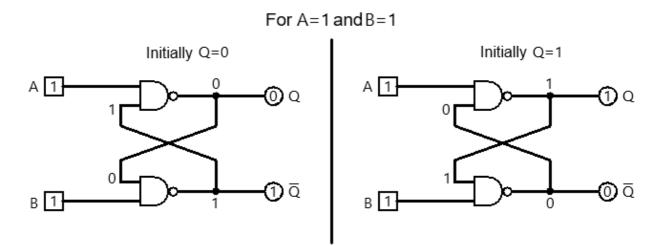

1)

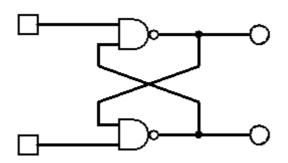

1.

For A=1 and B=0

Then we would have a Truth Table :

| Α | В | Q  | Q  |             |

|---|---|----|----|-------------|

| 0 | 0 | 1  | 1  | Not defined |

| 0 | 1 | 1  | 0  | Set to 1    |

| 1 | 0 | 0  | 1  | Reset to 0  |

| 1 | 1 | Q` | Q` | Memorize    |

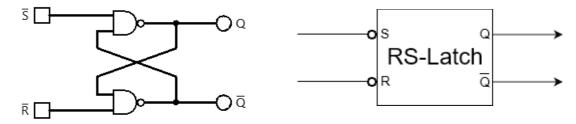

By observation, the truth table represents a RS-Latch circuit with  $A=\overline{S}$  et  $B=\overline{R}$

This is called a circuit  $\overline{R} \overline{S}$ -Latch

**Remark :** In modern circuits and for greater optimality, FlipFlops are implemented at the transistor level, so they are even smaller.

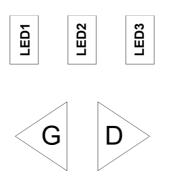

# Exercise 03 :

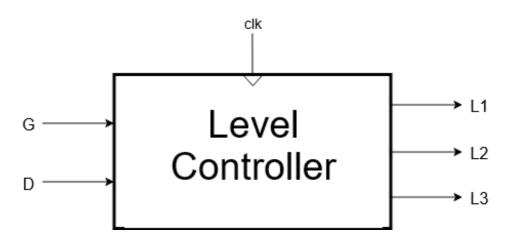

#### Step 2 : F.S.M.

S0  $\rightarrow$  All LEDs are off S1  $\rightarrow$  LED1 is on S2  $\rightarrow$  LED1 and LED2 are on S3  $\rightarrow$  All LEDs are on

$\begin{array}{l} \text{S0} \rightarrow \text{L1} = 0, \, \text{L2} = 0, \, \text{L3} = 0 \\ \text{S1} \rightarrow \text{L1} = 1, \, \text{L2} = 0, \, \text{L3} = 0 \\ \text{S2} \rightarrow \text{L1} = 1, \, \text{L2} = 1, \, \text{L3} = 0 \\ \text{S3} \rightarrow \text{L1} = 1, \, \text{L2} = 1, \, \text{L3} = 1 \end{array}$

**Remark 1:** The outputs should normally be represented inside the State circle, they have been listed below the F.S.M. for simplicity.

**Remark 2:** Events are described by Boolean expressions instead of binary values ( $\overline{GD} \Leftrightarrow G=0$ , D=1). This allows them to be reduced in writing and brings together several combinations of values under the same expression.

#### Step 3 : Transition Table

| Current State | G | D | Next State |

|---------------|---|---|------------|

|               | 0 | 0 | S0         |

| SO            | 0 | 1 | S1         |

| 30            | 1 | 0 | S0         |

|               | 1 | 1 | S0         |

|               | 0 | 0 | S1         |

| S1            | 0 | 1 | S2         |

| 51            | 1 | 0 | S0         |

|               | 1 | 1 | S1         |

|               | 0 | 0 | S2         |

| S2            | 0 | 1 | S3         |

| 52            | 1 | 0 | S1         |

|               | 1 | 1 | S2         |

|               | 0 | 0 | S3         |

| S3            | 0 | 1 | S3         |

| 33            | 1 | 0 | S2         |

|               | 1 | 1 | S3         |

**Remark :** Transition Table must contain all possible combinations of inputs.

# <u>Step 4</u> : Encoded States Table and Outputs Table

| State | <b>S</b> <sub>1</sub> | S <sub>0</sub> | L1 | L2 | L3 |

|-------|-----------------------|----------------|----|----|----|

| S0    | 0                     | 0              | 0  | 0  | 0  |

| S1    | 0                     | 1              | 1  | 0  | 0  |

| S2    | 1                     | 0              | 1  | 1  | 0  |

| S3    | 1                     | 1              | 1  | 1  | 1  |

**Remark :** The formulas of L1 and L2 and L3 can be extracted visually.

#### Step 5 : Encoded Transition Table

| S <sub>1</sub> | S <sub>0</sub> | G | D | S'1 | <b>S'</b> <sub>0</sub> |

|----------------|----------------|---|---|-----|------------------------|

| 0              | 0              | 0 | 0 | 0   | 0                      |

| 0              | 0              | 0 | 1 | 0   | 1                      |

| 0              | 0              | 1 | 0 | 0   | 0                      |

| 0              | 0              | 1 | 1 | 0   | 0                      |

| 0              | 1              | 0 | 0 | 0   | 1                      |

| 0              | 1              | 0 | 1 | 1   | 0                      |

| 0              | 1              | 1 | 0 | 0   | 0                      |

| 0              | 1              | 1 | 1 | 0   | 1                      |

| 1              | 0              | 0 | 0 | 1   | 0                      |

| 1              | 0              | 0 | 1 | 1   | 1                      |

| 1              | 0              | 1 | 0 | 0   | 1                      |

| 1              | 0              | 1 | 1 | 1   | 0                      |

| 1              | 1              | 0 | 0 | 1   | 1                      |

| 1              | 1              | 0 | 1 | 1   | 1                      |

| 1              | 1              | 1 | 0 | 1   | 0                      |

| 1              | 1              | 1 | 1 | 1   | 1                      |

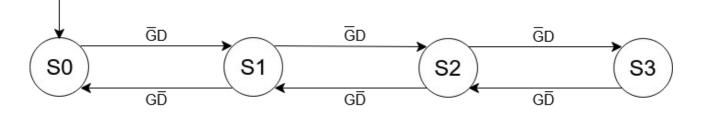

### Step 6 : Logic Formulas

$L1 = S_1 + S_0$  $L2 = S_1$  $L3 = S_1 \cdot S_0$

```

S'_{1}(S_{1},S_{0},G,D) = S_{1} \cdot \overline{G} + S_{1} \cdot D + S_{1} \cdot S_{0} + S_{0} \cdot \overline{G} \cdot D

```

| S <sub>1</sub> S <sub>0</sub> |    |    |    |    |

|-------------------------------|----|----|----|----|

| GD                            | 00 | 01 | 11 | 10 |

| 00                            | 0  | 1  | 1  | 0  |

| 01                            | 1  | 0  | 1  | 1  |

| 11                            | 0  | 1  | 1  | 0  |

| 10                            | 0  | 0  | 0  | 1  |

```

\begin{split} \mathbf{S'}_{0}(\mathbf{S}_{1},\mathbf{S}_{0},\mathbf{G},\mathbf{D}) &= \overline{\mathbf{S}}_{0} \cdot \overline{\mathbf{G}} \cdot \mathbf{D} + \mathbf{S}_{0} \cdot \overline{\mathbf{G}} \cdot \overline{\mathbf{D}} + \\ \mathbf{S}_{1} \cdot \overline{\mathbf{G}} \cdot \mathbf{D} + \mathbf{S}_{0} \cdot \mathbf{G} \cdot \mathbf{D} + \mathbf{S}_{1} \cdot \overline{\mathbf{S}}_{0} \cdot \mathbf{G} \cdot \overline{\mathbf{D}} \end{split}

```

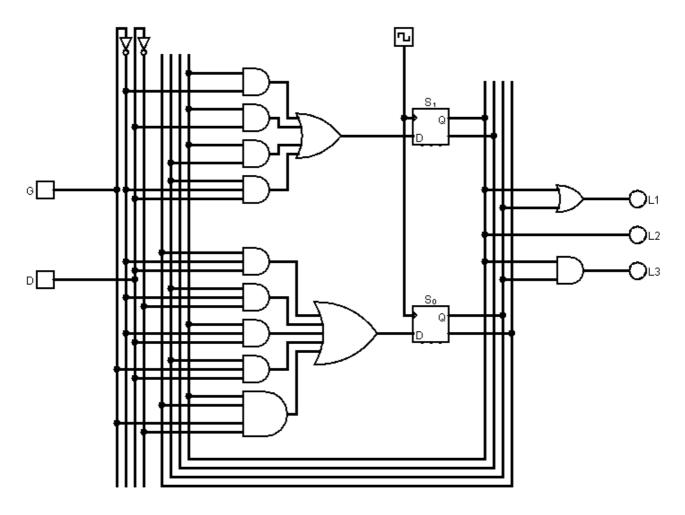

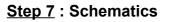

#### Step 7 : Schematics

2) When the user presses both buttons at the same time the State will not change, it is also equivalent to when the user does not press any button. This operation is not shown on the F.S.M. Usually, a Transition looping upon the same State must be drown to illustrate these 2 cases, but to not clutter up the F.S.M. too much they have been omitted.

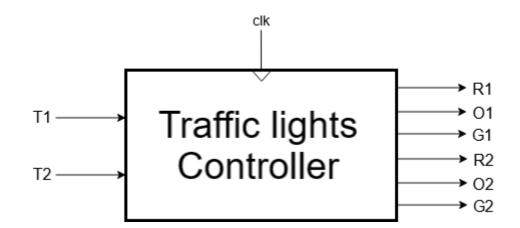

### Exercise 04 :

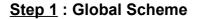

### 1) <u>Step 1</u> : Global Scheme

- T : Timer

- R : Red color

- O : Orange color

- G : Green color

R1, O1, G1 : lights of F1 and F4 R2, O2, G2 : lights of F2 and F3

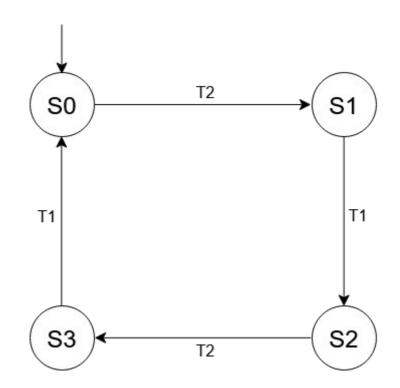

#### Step 2 : F.S.M.

- $\begin{array}{l} \text{S0} \rightarrow \text{R1=1, O1=0, G1=0 (F1 and F4 are red)} \\ \text{R2=0, O2=0, G2=1 (F2 and F3 are green)} \end{array}$

- $S1 \rightarrow R1=1, O1=0, G1=0$  (F1 and F4 are red) R2=0, O2=1, G2=0 (F2 and F3 are orange)

- $S2 \rightarrow R1=0, O1=0, G1=1$  (F1 and F4 are green) R2=1, O2=0, G2=0 (F2 and F3 are red)

- $S3 \rightarrow R1=0, O1=1, G1=0$  (F1 and F4 are orange) R2=1, O2=0, G2=0 (F2 and F3 are red)

**Remark 1:** Timer 1 will produce a 1 at the end of each 30 seconds, this will trigger the circuit to switch from red to green and vice versa. Timer 2 is also 30 seconds, it is shifted 27 seconds behind, or 3 seconds ahead (since it is a periodic signal) compared to Timer 1. It is responsible for the timing of the orange light.

**Remark 2:** The signals R1, O1 and G1 are identical for F1 and F4. And the same for R2, O2 and V2 with F2 and F3.

| Current State | T1 | T2 | Next State |

|---------------|----|----|------------|

|               | 0  | 0  | SO         |

| SO            | 0  | 1  | S1         |

| 30            | 1  | 0  | -          |

|               | 1  | 1  | -          |

|               | 0  | 0  | S1         |

| S1            | 0  | 1  | -          |

| 51            | 1  | 0  | S2         |

|               | 1  | 1  | -          |

|               | 0  | 0  | S2         |

| S2            | 0  | 1  | S3         |

| 32            | 1  | 0  | -          |

|               | 1  | 1  | -          |

|               | 0  | 0  | S3         |

| S3            | 0  | 1  | -          |

| 33            | 1  | 0  | SO         |

|               | 1  | 1  | -          |

#### Step 3 : Transition Table

**Remark 1:** T1 and T2 are Timers and it is impossible according to the arrangement of our circuit for the signals T1 and T2 to arrive at the same time, or for T2 to exceed T1. These impossible cases are represented by many *don't care* in the table which will help us later in the minimization.

**Remark 2:** For simplicity, the loop Transitions for the case T1=0, T2=0 in all 4 States, were not represented on the F.S.M. But these Transitions are real and they must be taken into consideration in the Transition Table .

**Remark 3:** Often looped Transitions that do not change the State are ignored in the F.S.M. But they are always implmented in the Transition Table.

<u>Step 4</u> : Encoded States Table and Outputs Table

| States | S <sub>1</sub> | S <sub>0</sub> | R1 | 01 | V1 | R2 | 02 | V2 |

|--------|----------------|----------------|----|----|----|----|----|----|

| S0     | 0              | 0              | 1  | 0  | 0  | 0  | 0  | 1  |

| S1     | 0              | 1              | 1  | 0  | 0  | 0  | 1  | 0  |

| S2     | 1              | 0              | 0  | 0  | 1  | 1  | 0  | 0  |

| S3     | 1              | 1              | 0  | 1  | 0  | 1  | 0  | 0  |

## Step 5 : Encoded Transition Table

| S <sub>1</sub> | S <sub>0</sub> | T1 | T2 | S'1 | <b>S'</b> 0 |

|----------------|----------------|----|----|-----|-------------|

| 0              | 0              | 0  | 0  | 0   | 0           |

| 0              | 0              | 0  | 1  | 0   | 1           |

| 0              | 0              | 1  | 0  | -   | -           |

| 0              | 0              | 1  | 1  | -   | -           |

| 0              | 1              | 0  | 0  | 0   | 1           |

| 0              | 1              | 0  | 1  | -   | -           |

| 0              | 1              | 1  | 0  | 1   | 0           |

| 0              | 1              | 1  | 1  | -   | -           |

| 1              | 0              | 0  | 0  | 1   | 0           |

| 1              | 0              | 0  | 1  | 1   | 1           |

| 1              | 0              | 1  | 0  | -   | -           |

| 1              | 0              | 1  | 1  | -   | -           |

| 1              | 1              | 0  | 0  | 1   | 1           |

| 1              | 1              | 0  | 1  | -   | -           |

| 1              | 1              | 1  | 0  | 0   | 0           |

| 1              | 1              | 1  | 1  | -   | -           |

#### <u>Step 6</u> : Logical Formulas

$R1(S_{1},S_{0}) = \overline{S}_{1}$   $O1(S_{1},S_{0}) = S_{1} \cdot S_{0}$   $V1(S_{1},S_{0}) = S_{1} \cdot \overline{S}_{0}$   $R2(S_{1},S_{0}) = S_{1}$   $O2(S_{1},S_{0}) = \overline{S}_{1} \cdot S_{0}$   $V2(S_{1},S_{0}) = \overline{S}_{1} + S_{0}$

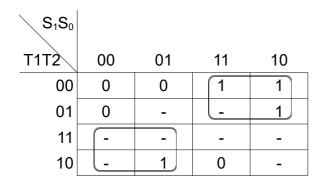

| S <sub>1</sub> S <sub>0</sub> |    |    |     |    |

|-------------------------------|----|----|-----|----|

| T1T2                          | 00 | 01 | 11  | 10 |

| 00                            | 0  | 1  | 1   | 0  |

| 01                            | 1  | _  | - ) | 1  |

| 11                            | -  | -  | -   |    |

| 10                            | -  | 0  | 0   | -  |

$$S'_{1}(S_{1},S_{0},T1,T2) = S_{1} \cdot \overline{T1} + \overline{S}_{1} \cdot T1 = S_{1} \oplus T1$$

$S'_{0}(S_{1},S_{0},T1,T2) = T2 + S_{0} \cdot \overline{T1}$

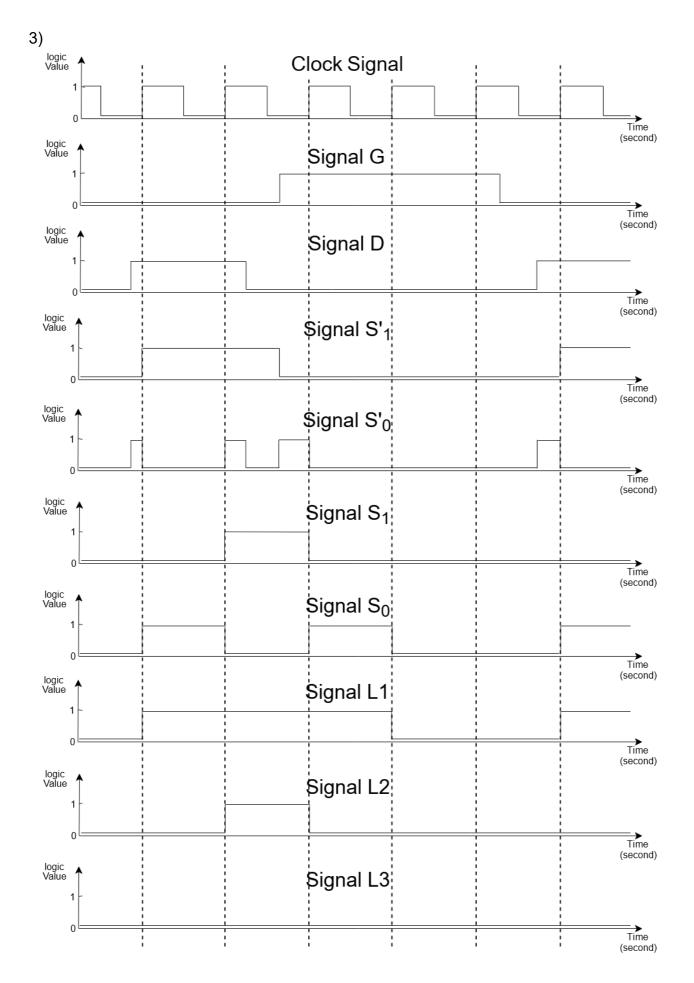

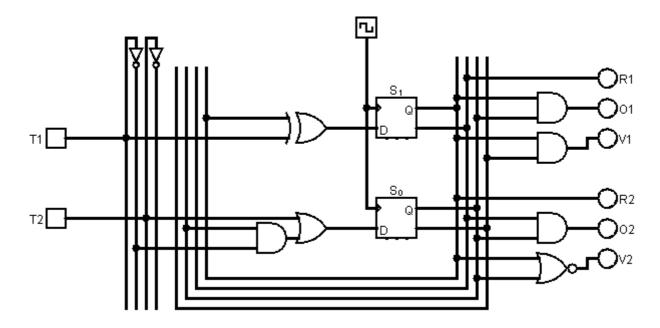

**Remark 1:** The frequency of the clock was not indicated in the exercise, but it can be deduced that the period cannot exceed 3 seconds, because the minimum signal change in the circuit is 3 seconds, that of the orange light. We chose 1 second as the period, therefore a frequency of 1 Hertz.

**Remark 2:** The signals from the 2 Timers are shifted and advanced by half a period compared to the clock signal, this gives enough time for the D-FlipFlop and the signal in the combinational circuits to propagate correctly.

**Remark 3:** Tracking the signals from the memory cells and the Output Combinational Output Circuit are quite easy, they are fixed over an entire period. On the other hand, the signals  $S'_1$  and  $S'_0$  of the Next State Combinational Circuit are more difficult to follow, because they must be updated with each change in the inputs T1 and T2 and in the memory cells  $S_1$  and  $S_0$ .

**Remark 4:** To avoid too many complications in the chronogram, the signals  $S'_1$  and  $S'_0$  were not updated in the small part of the half-period after T1 and T2.

## Exercise 05 :

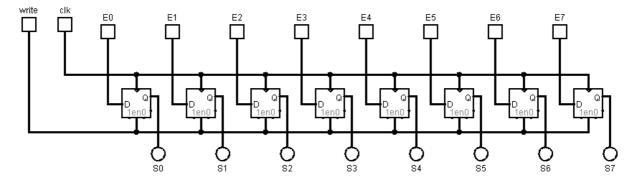

1) The 8-bit Register circuit with the Write command :

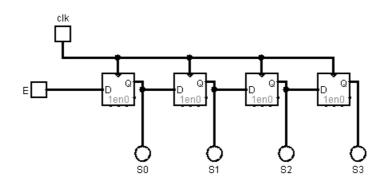

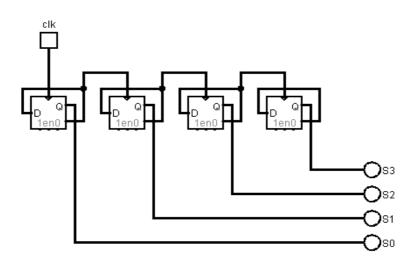

2) The 4-bit SIPO Shift circuit :

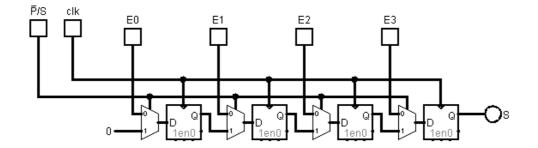

The 4-bit PISO Shift circuit :

**Remark 1:** The  $\overline{P}/S$  (Parallel/Serial) control input allows to choose between, entering the 4 inputs in parallel, or shifting the values in a chain through the cells to output them in series on the S output.

**Remark 2:** The bar in  $\overline{P}/S$  indicates which functionality is chosen by the value 0, so if the input is set to 0 the Parallel input will be used.

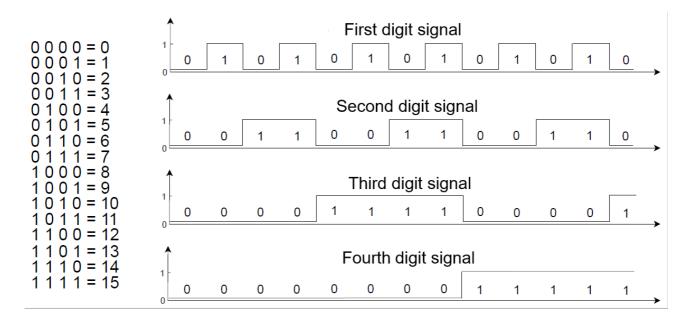

3) To build a Counter we must carefully study and observe the binary format of the increment operation. We can see the numbers incrementing in the left part of the figure below :

If we focus on a single column for a given digit, for example on the first digit. We can observe that it is a periodic signal identical to the clock signal. As well as for the second column, with the difference that it is double the first. And the third is also double the second, and so on and so forth. The signals of all its 4-bit digits are transcribed in the right part of the above figure.

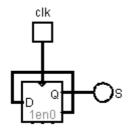

So to create a Counter, we simply need to generate a clock signal for each digit, with the condition that the next digit must double the period of the previous digit. To create a clock signal it's quite simple, just use a D-FlipFlop as shown in the diagram below. The  $\overline{Q}$  output must loop to the D input, so for each Rising Edge the FlipFlop will take the inverse value of the current value.

To make the signal of digit taking twice the period of the previous digit, we simply use the output of the previous digit as a clock for the current digit. As in the figure below. You note that in the figure we take the signal  $\overline{Q}$  instead of Q. Because by observing previous graph of the signals above, we notice that the digital signal really changes value during the Falling Edge of the previous digital signal. This forces us to use the inverse signal  $\overline{Q}$  instead of Q.

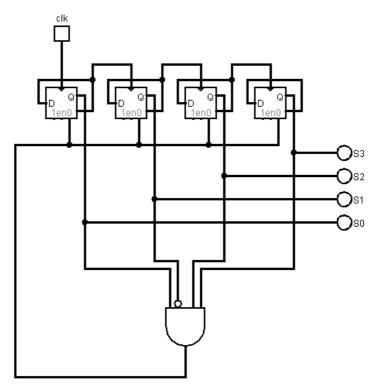

To limit the count to the value 12 (1100), it is wise to use the FlipFlip Reset command which will reset all the FlipFlops to 0 when the circuit detects that it has reached the limit. The limit in our case should be the value 13, the value just after 12, which should simply be detected by an AND gate. The Reset used here is Asynchronous, so it will reset the cell immediately after detecting the value 13. It practically instantaneous, the counter will never get enough time to hold the value 13.

The diagram of a 4-bit counter that counts up to the value 12 :

**Remark 3:** The Reset in this solution is supposed to be Asynchronous, if it was a Synchronous command the solution should be different.

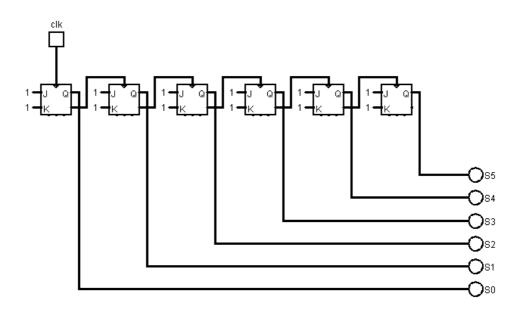

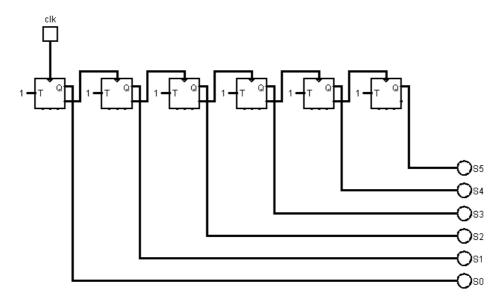

4) The 6-bit counter circuit based on JK-FlipFlop :

The 6-bit counter circuit based on T-FlipFlop :

**Remark 4:** The Counter has the ability to oscillate its outputs by doubling the period for each output, which gives it the ability to be used very often as a frequency divider. For example, if you apply a frequency of 1 KHz to its clock, the first output will produce a signal of 500 Hz, the second of 250 Hz, the third of 125 Hz, and so on.

**Remark 5:** The 3 fairly simple types of Counters that we have just built are most often called Asynchronous Counters, or Ripple Counters. Due to the fact that the output of one cell is the clock of the next, which will cause a small clock delay that accumulate across the cells. For low frequency circuits below 1 MHz, normally this should not pose a problem. But for high frequency circuits they become a source of failure, then so-called Synchronous Counters which are more complex are generally more reliable. Synchronous implies that all cells use the same clock signal.